數(shù)字集成電路版圖設(shè)計入門 從Cadence IC原理圖繪制到仿真驗證

數(shù)字集成電路(IC)是現(xiàn)代電子系統(tǒng)的核心,其設(shè)計流程是一個從抽象到具體、從邏輯到物理的嚴謹過程。其中,版圖設(shè)計是連接電路設(shè)計與實際芯片制造的橋梁。本文將以業(yè)界廣泛使用的Cadence設(shè)計平臺為例,簡要介紹數(shù)字IC版圖設(shè)計的前期關(guān)鍵步驟:原理圖繪制與電路仿真。

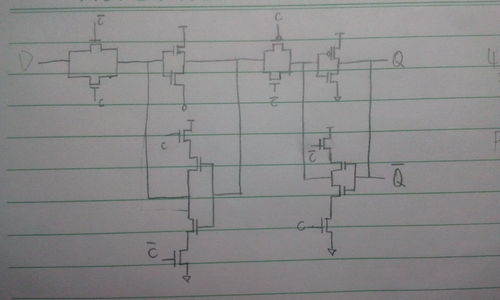

一、原理圖繪制:設(shè)計的藍圖

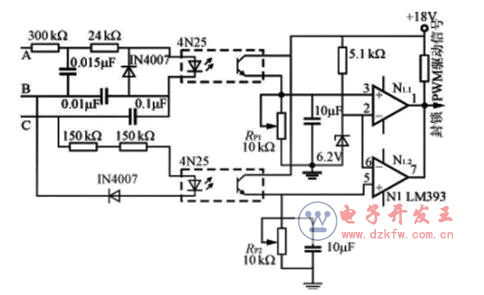

原理圖繪制是數(shù)字IC設(shè)計的起點,它使用圖形化的符號(如與門、或門、觸發(fā)器、晶體管等)來清晰地描述電路的邏輯功能和連接關(guān)系。在Cadence IC設(shè)計環(huán)境中(如Virtuoso Schematic Editor),工程師可以:

1. 調(diào)用單元庫:從標準單元庫或定制庫中選取所需的邏輯門或功能模塊。

2. 進行連接:通過導線(Wire)將各個元器件的端口按照設(shè)計規(guī)范連接起來,形成完整的電路網(wǎng)絡(luò)。

3. 定義屬性:為電源、地、輸入輸出端口以及關(guān)鍵信號線設(shè)置電壓、驅(qū)動強度等屬性。

一個清晰、準確的原理圖是后續(xù)所有工作的基礎(chǔ),它不僅體現(xiàn)了設(shè)計者的意圖,也是團隊溝通和設(shè)計審查的重要文檔。

二、電路仿真:功能的驗證

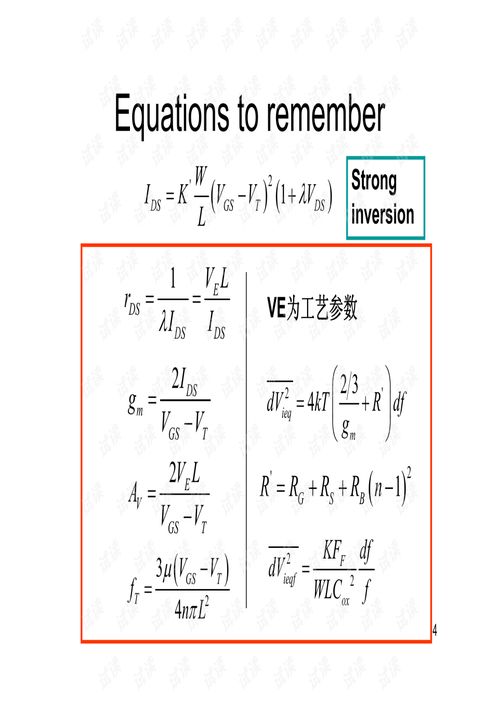

完成原理圖繪制后,必須通過仿真來驗證電路的功能和時序是否正確,這一步在流片(Tape-out)前至關(guān)重要。在Cadence平臺中,通常使用Spectre或APS等仿真器配合ADE(Analog Design Environment)環(huán)境進行。仿真主要包含:

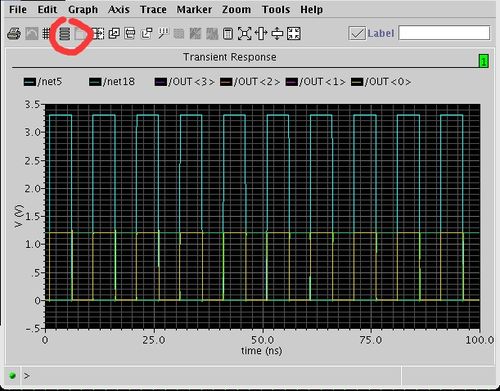

- 功能仿真:驗證電路在理想情況下的邏輯行為是否與設(shè)計規(guī)格書一致。工程師需要搭建測試平臺(Testbench),為電路提供各種輸入激勵(如時鐘、數(shù)據(jù)信號),并觀察輸出響應(yīng)。

- 時序仿真:在功能正確的基礎(chǔ)上,引入標準單元庫或晶體管模型提供的時序信息(如延遲、建立保持時間),驗證電路在指定工作頻率下是否能正確工作,排查是否存在時序違規(guī)(Timing Violation)。

- 仿真結(jié)果分析:利用波形查看工具(如Virtuoso Visualization & Analysis)觀察信號波形,測量關(guān)鍵路徑延遲,確保電路滿足所有性能指標。

銜接與展望:從仿真到版圖

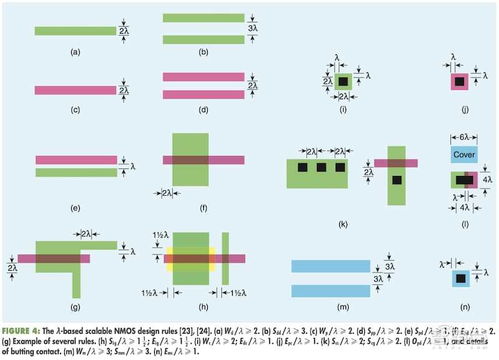

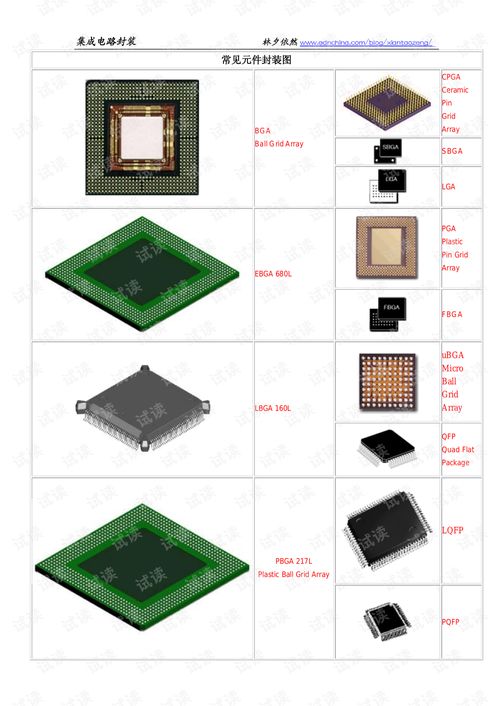

成功的原理圖與仿真是后續(xù)物理版圖設(shè)計的前提。只有經(jīng)過充分驗證的電路,才能進入版圖實現(xiàn)階段,即根據(jù)工藝廠的設(shè)計規(guī)則,將邏輯電路轉(zhuǎn)化為由幾何圖形(多邊形)構(gòu)成的物理掩膜版圖。這個過程同樣在Cadence Virtuoso等工具中完成,涉及布局、布線、設(shè)計規(guī)則檢查(DRC)、版圖與原理圖對照(LVS)等一系列復雜步驟。

掌握Cadence IC工具進行原理圖繪制與仿真是數(shù)字集成電路設(shè)計工程師的基本功。它確保了設(shè)計在邏輯和時序上的正確性,為最終高性能、高可靠性的芯片實現(xiàn)奠定了堅實基石。

如若轉(zhuǎn)載,請注明出處:http://www.viqq.cn/product/46.html

更新時間:2026-02-22 08:14:57