超大規(guī)模集成電路設(shè)計(jì)規(guī)則 通往微觀世界的施工藍(lán)圖

在當(dāng)今信息時(shí)代的核心,超大規(guī)模集成電路(VLSI)如同電子系統(tǒng)的精密大腦,驅(qū)動(dòng)著從智能手機(jī)到超級計(jì)算機(jī)的一切。而構(gòu)筑這些包含數(shù)十億晶體管的微觀世界的基石,正是一套嚴(yán)謹(jǐn)、詳盡的設(shè)計(jì)規(guī)則。這些規(guī)則并非簡單的建議,而是確保芯片功能、性能與可制造性的鐵律。它們界定了物理布局的極限,是連接芯片設(shè)計(jì)理想與硅片制造現(xiàn)實(shí)之間的關(guān)鍵橋梁。

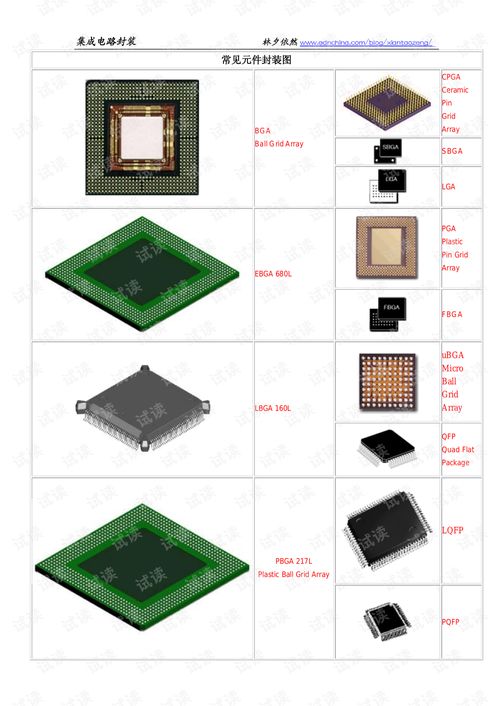

設(shè)計(jì)規(guī)則的核心理念與分類

設(shè)計(jì)規(guī)則本質(zhì)上是代工廠(如臺(tái)積電、三星)提供給芯片設(shè)計(jì)公司(如蘋果、高通)的一套幾何與電氣約束規(guī)范。其根本目的是在給定的半導(dǎo)體制造工藝下(如7納米、5納米),保證設(shè)計(jì)出的電路能夠被高良率、可靠地生產(chǎn)出來。它主要解決光刻、蝕刻、離子注入等工藝步驟中固有的物理限制和偏差問題。

通常,設(shè)計(jì)規(guī)則可分為幾大類:

- 幾何設(shè)計(jì)規(guī)則(Geometric Design Rules):這是最直觀、最基礎(chǔ)的一類,直接規(guī)定了版圖中各種圖形(如晶體管、金屬連線、接觸孔)的尺寸、間距、覆蓋等幾何參數(shù)。例如:

- 最小寬度:一根金屬連線或一個(gè)晶體管柵極所允許的最小尺寸。這直接受到光刻分辨率極限的制約。

- 最小間距:兩個(gè)相同或不同層圖形之間必須保持的最小距離,以防止短路或因工藝偏差導(dǎo)致的橋接。

- 最小包圍/延伸:要求某一層圖形必須完全包圍或延伸超出另一層圖形一定距離。例如,接觸孔必須被金屬層完全包圍,確保可靠的電氣連接。

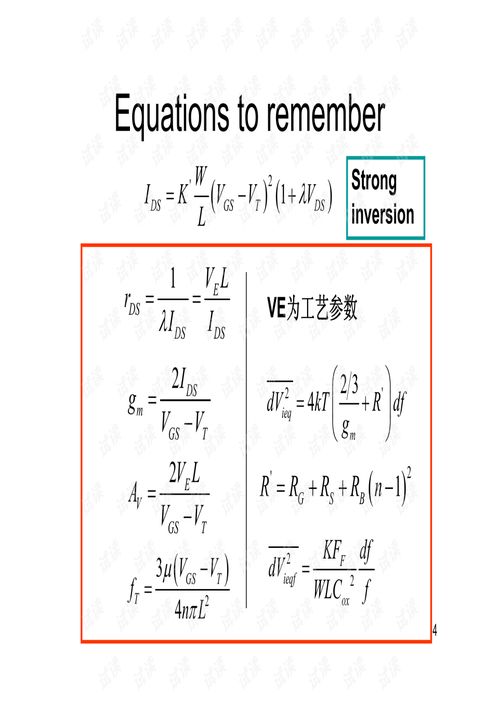

- 電氣設(shè)計(jì)規(guī)則(Electrical Design Rules):這些規(guī)則與電路的性能、功耗和可靠性直接相關(guān),通常基于幾何規(guī)則和工藝的電氣特性衍生而來。例如:

- 天線規(guī)則:防止在制造過程中,連接到晶體管柵極的金屬連線像“天線”一樣收集等離子刻蝕產(chǎn)生的電荷,從而擊穿脆弱的柵氧層。

- 電流密度規(guī)則:規(guī)定金屬連線的最大允許電流,防止因電遷移導(dǎo)致連線斷裂或性能退化。

- 寄生參數(shù)提取規(guī)則:指導(dǎo)如何從版圖幾何結(jié)構(gòu)中提取電阻、電容等寄生效應(yīng),用于精確的電路性能仿真。

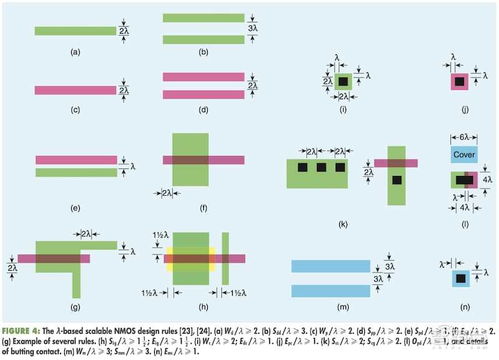

實(shí)例解析:從規(guī)則到版圖

以一張典型的VLSI設(shè)計(jì)規(guī)則示意圖為例(其概念源自業(yè)界通用實(shí)踐),我們可以直觀理解這些約束如何應(yīng)用。

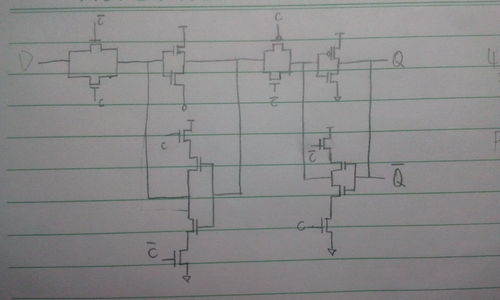

- 晶體管層級:對于構(gòu)成基本開關(guān)的MOSFET,規(guī)則會(huì)嚴(yán)格定義有源區(qū)(晶體管溝道所在)、多晶硅柵極(控制極)以及接觸孔(連接源/漏極與金屬線)之間的幾何關(guān)系。例如,多晶硅柵極必須與有源區(qū)充分交疊并兩端延伸一定長度,以確保形成完整的溝道并容忍對位偏差。

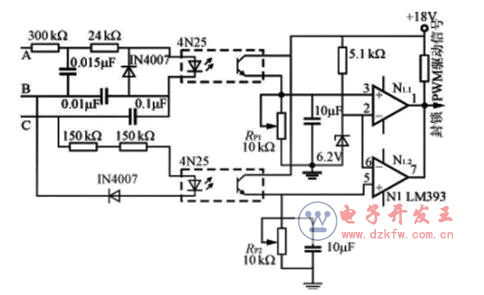

- 互連層級:現(xiàn)代芯片擁有多達(dá)十余層的金屬互連,像立交橋一樣將晶體管連接成系統(tǒng)。設(shè)計(jì)規(guī)則在這里尤為關(guān)鍵:

- 不同層金屬線之間有最小間距和最小寬度規(guī)定。

- 當(dāng)金屬線需要從一個(gè)層垂直連接到另一個(gè)層時(shí),需要通過通孔。規(guī)則會(huì)規(guī)定通孔的最小尺寸、通孔與上下層金屬的對齊要求、以及同一區(qū)域允許的通孔密度等。

- 對于長距離或承載大電流的電源/地線,規(guī)則可能要求使用更寬的金屬線或插入大量的通孔陣列以降低電阻和滿足電流密度要求。

- 密度規(guī)則:為了確保化學(xué)機(jī)械拋光(CMP)工序的均勻性,避免某些區(qū)域過度研磨或研磨不足,設(shè)計(jì)規(guī)則會(huì)要求芯片上不同區(qū)域的圖形(如金屬、絕緣層)保持一個(gè)全局的、均勻的密度分布。這常常需要通過添加無電氣功能的“冗余圖形”來滿足。

挑戰(zhàn)、演進(jìn)與未來

隨著工藝節(jié)點(diǎn)向3納米、2納米及以下推進(jìn),設(shè)計(jì)規(guī)則變得異常復(fù)雜和嚴(yán)苛。極紫外光刻(EUV)的引入、三維鰭式場效應(yīng)晶體管(FinFET)乃至環(huán)柵晶體管(GAA)等新結(jié)構(gòu)的應(yīng)用,都帶來了全新的規(guī)則類別。例如,對于FinFET,規(guī)則需要定義鰭的間距、高度以及與柵極的三維交互關(guān)系。

如今,純粹依賴人工手動(dòng)檢查設(shè)計(jì)規(guī)則已不可能。電子設(shè)計(jì)自動(dòng)化(EDA)工具扮演了核心角色,其設(shè)計(jì)規(guī)則檢查(DRC) 功能能夠自動(dòng)、徹底地掃描整個(gè)版圖數(shù)據(jù)庫,標(biāo)識(shí)出所有違反預(yù)定規(guī)則的地方,是芯片流片前不可或缺的“體檢”關(guān)卡。

超大規(guī)模集成電路的設(shè)計(jì)規(guī)則是物理學(xué)、材料科學(xué)、精密制造與電子工程的結(jié)晶。它們?nèi)缤徊繕O其精密的微觀世界“建筑法典”,每一代工藝的演進(jìn)都伴隨著這部法典的增補(bǔ)與修訂。正是這些看似繁瑣的條條框框,約束并指引著工程師們在方寸之間,構(gòu)建出改變世界的強(qiáng)大算力。

如若轉(zhuǎn)載,請注明出處:http://www.viqq.cn/product/64.html

更新時(shí)間:2026-02-22 18:50:39